# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111462651 A (43)申请公布日 2020.07.28

(21)申请号 202010351855.4

(22)申请日 2020.04.28

(30)优先权数据

16/406196 2019.05.08 US

(71)申请人 伊乐视有限公司 地址 美国华盛顿州(邮编98683)温哥华市 东南第34号大街18110号480号间

(72)**发明人** 保罗•约翰•舒勒 战长青 佐佐木健司 葛特鄂孟 李宗霑

(74)专利代理机构 深圳市赛恩倍吉知识产权代理有限公司 44334

代理人 汪飞亚

(51) Int.CI.

*G09F 9/33*(2006.01) *H01L 27/15*(2006.01)

权利要求书2页 说明书19页 附图20页

### (54)发明名称

用于表面贴装微型LED流体组装的发光显示 基板及制备方法

#### (57)摘要

用于表面贴装微型LED流体组装的发光显示基板及其制备方法被提出。该发光显示基板包括:支撑基板,具有平面的顶表面以及包括列和行导线的阵列的发光二极管(LED)交叉点控制矩阵;第一薄膜层,覆盖所述支撑基板的顶表面且包括多个阱;其中,每个阱具有凸的底表面、与对应的列导线连接的第一基板电极、以及与对应的行导线连接的第二基板电极。

1.一种发光显示基板,其特征在于,包括:

支撑基板,具有平面的顶表面以及包括列和行导线的阵列的发光二极管(LED)交叉点控制矩阵;

第一薄膜层,覆盖所述支撑基板的顶表面且包括多个阱;

其中,每个阱具有凸的底表面、与对应的列导线连接的第一基板电极、以及与对应的行导线连接的第二基板电极。

- 2. 如权利要求1所述的发光显示基板,其特征在于:所述发光显示基板进一步包括:

- 位于所述支撑基板的顶表面和第一薄膜层之间的第二薄膜层;

- 位于所述支撑基板的顶表面和第二薄膜层之间且位于每个阱底部下方的垫片。

- 3.如权利要求2所述的发光显示基板,其特征在于:所述第一薄膜层的每个阱具有第一直径:

其中,所述垫片具有小于第一直径的宽度和一顶表面;

其中,所述阱的凸的底表面是由于所述垫片的顶表面和所述支撑基板的顶表面之间的 高度差。

- 4.如权利要求2所述的发光显示基板,其特征在于:所述垫片选自导电材料和电绝缘材料。

- 5.如权利要求2所述的发光显示基板,其特征在于:所述第一基板电极是具有用于电连接微型LED的第一电界面表面的中心基板电极,且所述第二基板电极是具有第二电界面表面的周边基板电极,相对于所述支撑基板的顶表面所界定的,所述第二电界面表面比所述第一电界面表面更低且用于电连接微型LED。

- 6.如权利要求2所述的发光显示基板,其特征在于:所述垫片直接覆盖所述列导线,形成一列互连垫片;

其中,所述第二薄膜层包括覆盖所述列互连垫片的过孔;以及

其中,所述第一基板电极是覆盖所述过孔并连接所述列互连垫片的中心基板电极。

7. 如权利要求5所述的发光显示基板,其特征在于:所述发光显示基板进一步包括:填充所述多个阱的多个表面贴装微型LED,

每个微型LED具有带有中心第一电极和周边第二电极的顶表面以及分别连接所述第一基板电极和所述第二基板电极的基板界面表面。

- 8.如权利要求7所述的发光显示基板,其特征在于:所述微型LED的中心第一电极和周边第二电极具有共面的基板界面表面。

- 9.如权利要求8所述的发光显示基板,其特征在于:所述表面贴装微型LED选自中心发光、周边发光和全区域发光的微型LED。

- 10.如权利要求7所述的发光显示基板,其特征在于:所述微型LED的中心第一电极和周边第二电极基板的基板界面表面不是共面的。

- 11.一种制备发光显示基板的方法,其特征在于,包括:

提供支撑基板,其具有平面的顶表面以及包括列和行导线的阵列的发光二极管(LED) 交叉点控制矩阵;

形成覆盖所述支撑基板的顶表面的凸的阱底部结构的阵列;

形成覆盖所述支撑基板的顶表面和凸的阱底部结构的第一薄膜层;以及

在所述第一薄膜层中形成多个阱,从而暴露出凸的阱底部结构。

- 12. 如权利要求11所述的方法,其特征在于:形成所述凸的阱底部结构的阵列包括:对于每个凸的阱底部结构,形成电连接对应的列导线的第一基板电极和电连接对应的行导线的第二基板电极。

- 13. 如权利要求12所述的方法,其特征在于:形成所述凸的阱底部结构的阵列包括: 在形成所述第一薄膜层之前,形成覆盖所述支撑基板的顶表面的垫片的阵列;以及 形成覆盖所述垫片的阵列的第二薄膜层。

- 14. 如权利要求13所述的方法,其特征在于:形成所述垫片的阵列包括形成具有宽度和 顶表面的垫片;

- 其中,在所述第一薄膜层中形成多个阱包括形成直径大于所述垫片宽度的多个阱;以 及

- 其中,所述阱的凸的底表面的形状响应于所述垫片的顶表面和所述支撑基板的顶表面 之间的高度差。

- 15. 如权利要求13所述的方法,其特征在于:形成所述垫片的阵列包括由选自导电和电绝缘材料的材料形成垫片。

- 16. 如权利要求12所述的方法,其特征在于:形成所述凸的阱底部结构的阵列包括:

形成具有用于电连接微型LED的第一电界面表面的中心第一基板电极;以及

形成具有第二电界面表面的周边第二基板电极,相对于支撑基板的顶表面所界定的, 所述第二电界面表面比第一电界面表面更低且用于电连接微型LED。

17. 如权利要求16所述的方法,其特征在于:形成所述垫片的阵列包括:

形成直接覆盖所述列导线的每个垫片,形成列互连垫片;

其中,形成所述第二薄膜层包括在所述第二薄膜层中形成覆盖每个列互连垫片的过 孔,以及

其中,形成所述中心第一基板电极包括形成覆盖所述过孔并电连接所述列互连垫片的中心第一基板电极。

- 18. 如权利要求11所述的方法,其特征在于:所述方法进一步包括:流体沉积多个表面贴装微型LED于所述多个阱中。

- 19.如权利要求18所述的方法,其特征在于:沉积所述多个表面贴装微型LED包括用多个微型LED填充所述多个阱,所述微型LED具有带有中心第一电极和周边第二电极的顶表面和分别连接第一基板电极和第二基板电极的基板界面表面。

- 20.如权利要求19所述的方法,其特征在于:沉积所述多个表面贴装微型LED包括沉积 具有中心第一电极和周边第二电极共面基板界面表面的微型LED。

- 21.如权利要求20所述的方法,其特征在于:沉积所述多个表面贴装微型LED包括沉积选自中心发光、周边发光和全区域发光的微型LED。

- 22. 如权利要求19所述的方法,其特征在于:沉积所述多个表面贴装微型LED包括沉积具有非共面中心第一电极和周边第二电极基板界面表面的微型LED。

# 用于表面贴装微型LED流体组装的发光显示基板及制备方法

## 技术领域

[0001] 本发明总体上涉及显示技术,更具体地涉及具有改善的电极界面表面平整度的表面贴装(SM) 无机微型发光二极管(µLED)的设计。

## 背景技术

[0002] 彩色显示器由发射与可见光红色、绿色和蓝色对应的三种波长的光的像素组成,这种被称为RGB显示器。像素的RGB元件以有序的方式打开和关闭,以累加产生可见光谱的颜色。有几种可以不同方式生成RGB图像的显示类型。液晶显示器(LCD)是最流行的技术,它们通过子像素的彩色滤光片照射白色光源(通常是荧光体产生的白色LED)来产生RGB图像。白光波长的某些部分被吸收,而另一些则穿过滤色镜透射彩色滤光片。有机发光二极管(OLED)显示器通过从有机发光材料内部以像素级别直接发射那些波长的每个波长的光来产生RGB光。有机发光二极管(OLED)显示器通过从有机发光材料内部以像素级别直接发射那些波长的每个波长的光来产生RGB光。

[0003] 第三种显示技术是微型LED显示器。该显示技术使用微米级(直径为10至150µm)的无机LED来直接发射像素级的光。为了使用微型LED制造RGB显示器,须组装分别在每个RGB波长范围内发光的三种不同类型的微型LED的大面积阵列。微型LED显示器的低成本制造需要使用大规模并行流体组装技术,以将数百万个单独的微型LED放置在规则的阵列中。当前具有HDTV分辨率的主流电视具有600万像素,而更高分辨率的4K和8K标准分别具有25和99百万像素。

[0004] 为了生产具有适当亮度的高产量低成本显示器,流体组装技术对微型LED结构提出了一些独特的要求,本文将讨论其中的一些。实用的显示技术须解决显示器以不同尺寸和分辨率制造的现实,因此要求像素尺寸的灵活性,从个人设备的每英寸300像素(ppi)到非常高的10-20ppi大型公共信息显示应用。显示屏亮度要求也因应用不同而有所不同,手机显示屏需要300尼特(每平方米的坎德拉),电视机需要1000尼特,而户外信息显示屏则需要5000尼特。因此,micro-LED技术须适应广泛的分辨率和亮度要求,同时仍保持使用流体组装所必需的物理性能。

[0005] 用于普通照明的基于氮化镓(GaN)的蓝色LED和用于各种指示灯的铝镓磷化(A1GaInP)红色LED的开发已经发展了许多代且这些工艺可以以非常低的成本生产出可靠的高效器件。因此,也许最重要的要求是微型LED结构须与商用无机LED的常规金属有机化学气相沉积(MOCVD)制造兼容。LED制造中有许多可能的变体,因此,本概述仅提供一个非常简短的概述,以识别制造高质量LED所需的因素,同时还描述了传统LED与此处所述的微型LED之间的特有的区别。由张和刘(Ning Zhang和Zhiqiang Liu,"InGaN材料系统和蓝/绿色发光体",in Li,Jinmin、Zhang,G.Q.(编),发光二极管,固态照明技术和应用系列4(Springer,Switzerland,2019))和Wang等人的基于A1GaInP的红色LED(Guohong Wang、Xiaoyan Yi、Teng Zhan和Yang Huang,"A1GaInP/A1GaAs材料系统和红色/黄色LED",in Li,Jinmin,Zhang,G.Q.(编),发光二极管,固态照明技术和应用系列4(Springer,

Switzerland,发明人:Schuele,Zhan,Sasaki,Ulmer和Lee 2019)是常规LED技术在可见光谱中的有用总结。

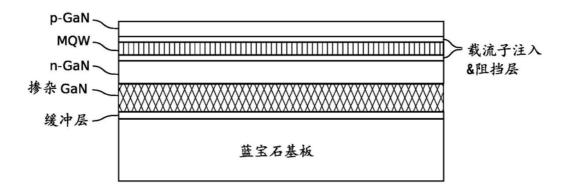

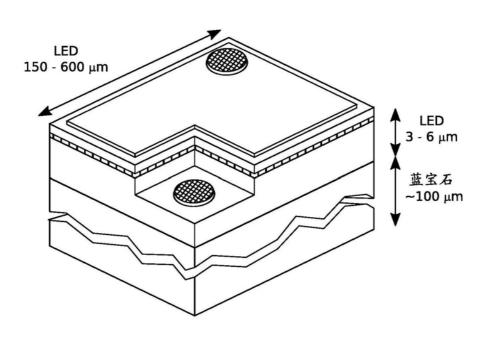

[0006] 图1A至1C是描绘用于一般照明目的的GaN LED晶片的图(现有技术)。发蓝光(约440纳米(nm))和绿光(约530nm)的GaN基LED以一系列复杂的高温MOCVD步骤被制造,以产生图1A的横截面所示的垂直LED结构。在直径为50至200毫米(mm)的抛光蓝宝石、硅(Si)或碳化硅(SiC)的生长基板上进行制造。通过沉积可选的AIN缓冲层和未掺杂的GaN来制备表面,以产生具有低缺陷和GaN晶格常数的晶体表面。此初始沉积的厚度和温度被调整以补偿生长基板和GaN之间的晶格失配。表面重量随厚度的增加而提高,因此高效器件的厚度超过约3微米(μm)。由于MOCVD沉积工艺复杂且昂贵,因此重要的是优化微型LED工艺以最有效地利用生长晶片(生长基板)的整个区域。

[0007] 在初始生长以制备晶体GaN表面之后,生长第一LED层并添加Si掺杂以生产用于阴极的n+GaN (n-GaN)。可选地,该叠层可以包括为电子注入和空穴阻挡而调整的层。接下来,用氮化铟镓 ( $In_xGa_{1-x}N$ )和GaN的交替层沉积多量子阱 (MQW)结构,其中铟含量和层的厚度决定了器件的发射光的波长。铟含量的增加将发射峰移动至更长的波长,但由于晶格失配也会增加内部应力,因此无法制造出高效率的GaN器件用于发红光,绿色发光器件的效率低于蓝色LED的效率。在MQW之后,叠层可以包括为电子阻挡和空穴注入而调整的层。最后,通过沉积掺杂镁 (Mg)的GaN形成p+阳极来完成MOCVD序列。

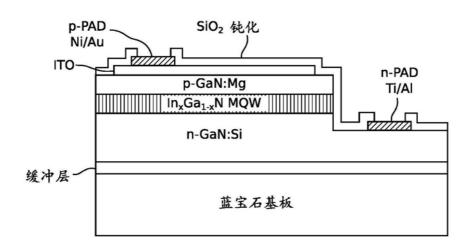

[0008] 完成的基板然后被图案化和蚀刻以形成单独的LED,且进行额外的处理以在阳极和阴极上形成电极,如图1B所示。在最简单的工艺流程中,通过沉积氧化镍(NiO<sub>x</sub>)的薄层以匹配p+GaN(p-GaN)功函数,然后沉积100至300nm厚度的铟锡氧化物(ITO)的层来形成透明导电电极。对该层进行图案化和蚀刻以在阳极上方形成电流扩散层。

[0009] 穿过叠层图案化并蚀刻一小块区域,使其与n+GaN接触。钝化层,通常为二氧化硅 (Si0<sub>2</sub>),被沉积以防止阳极和阴极之间发生泄漏电流,并在电极上方开设接触窗。电极 (通常由钛/铝 (Ti/A1) 制成) 被沉积以形成阴极接接触点,并添加可以是镍/金 (Ni/Au)、铬/金 (Cr/Au) 等的第二电极 (阳极)。通过研磨所述基板被减薄至约100 $\mu$ m,并通过切割或锯切将各个装置单个化。通过该工艺制造的装置通常为100 $\mu$ m,并且尺寸 (横截面) 为150至1000 $\mu$ m,例如如图1C所示。

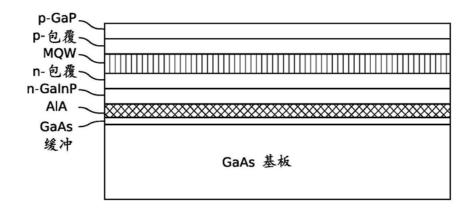

[0010] 图2A和图2B是示出用于制造红色发光指示器的砷化镓(GaAs)LED晶片的图(现有技术)。如图2A所示,基于GaAs材料系统使用明显不同的MOCVD工艺顺序制造高亮度红色LED。生长基板是几百微米厚的n掺杂GaAs晶片,被沉积的第一层是GaAs,以产生高质量的晶体表面。下一层是铝/砷化物(A1As),其随后将其用作释放层。LED叠层可以从可选的n掺杂分布式布拉格反射器(DBR)层或n掺杂GaInP窗口层和n掺杂A1GaInP包覆层开始。然后,在MQW活性区上沉积A1GaInP和A1GaAs的交替层,并对其厚度和成分进行调整,以使高效率LED在选定的波长下发光。活性区被A1GaInP的p掺杂覆层和p掺杂的GaInP窗口层覆盖以完成LED。A1As释放层上方的整个LED叠层的厚度可以为10至15μm。

[0011] GaAs生长基板与AlGaInP的MOCVD生长为晶格匹配的,但是GaAs吸光并且非常脆,这对于LED封装来说是严重的缺点。因此,如图2B所示,通过完全蚀刻基板或通过使用选择性湿蚀刻(通常为盐酸(HC1):乙酸)来对装置进行底切和释放,从而从基板上移除LED装置。在从基板上移除LED之前,通过电镀沉积铜的厚层用作散热器和每个装置的处理界面。首

先,金触击层被沉积且被图案化以定义铜区域,然后将铜电镀至约100μm的厚度。然后,在铜岛周围向下蚀刻LED叠层直到GaAs缓冲层,随后通过湿法蚀刻A1As层释放蚀刻底切装置。装置尺寸(横截面)类似于GaN一般照明LED的150至1000微米。

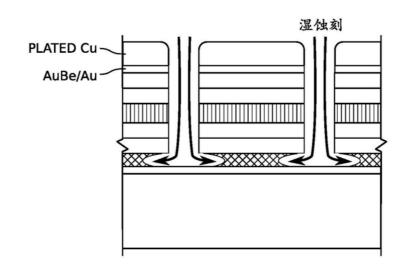

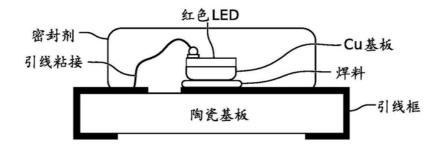

[0012] 图3A和3B分别描绘了传统的封装的蓝色和红色LED(现有技术)的局部截面图。呈现这些图是为了区别微型LED(在下面的详细说明中提供)和用于更大LED的常规封装技术。对于一般照明,由发蓝光的GaN装置产生白光,如图1B所示,具有覆盖LED并将某些蓝光转换为更长的波长的一个额外的颜色转换荧光体,通常是发出宽黄光的荧光体,例如掺有铈(III)的YAG(YAG:Ce³-或Y₃A1₅012:Ce³+)。所使用的封装具有用于进行电连接的引线框,用于消散LED中产生的热能的散热片以及将光导向用户的反射器。LED通过导热胶粘在散热片上,LED端子通过引线粘接连接引线框。粘接后,封装腔中会充满透明的密封剂,通常是硅树脂或环氧树脂,可保护装置免受机械损坏以及环境中空气和水的腐蚀。密封剂还可以包含颜色转换荧光体,或者荧光体可以在封装(未示出)上方的单独的膜中。包装完成后,将在称为重新分级(binning)的过程中测试设备的效率和峰值波长。如果该装置具有可接受的性能,则将其与阵列中的其他装置一起粘接到印刷电路板(PCB)上。重要的是要注意,照明阵列包含根据所需的工作电压和亮度串联、并联或串联/并联的多个装置。与要求每个像素具有可控制的亮度以产生图像的显示器阵列(例如电视或智能手机显示器)不同,普通照明阵列中的所有装置都同时工作。

[0013] 制造像素密度 (PPI) 在10至600范围内的显示器必然要求微型LED的横截面 (直径) 小于150微米。如以下更详细描述的,微型LED尺寸和内部结构是通过使用常规的光刻工艺来形成由掩模设计、膜厚和光刻胶曝光控制的图案而产生的。使用光刻图案作为掩模,蚀刻工艺选择性地去除材料以形成完整装置的特征。例如在GaN的情况下,跨越整个晶圆以及晶圆之间的蚀刻均不能完全均匀地进行,因此,创建具有共面N垫 (N-pad,连接n+半导体的电极) 和P垫 (P-pad,连接p+半导体的电极) 的结构所需的堆积量可能会有很大变化。堆积金属的沉积是通过蒸发或溅射进行的,并且厚度控制的精度甚至不如光刻步骤。如果微型LED的 N-pad和P-pad电极不共面,则微型LED与显示基板的电连接可能不完整,从而导致故障或高串联电阻。

[0014] 为了使使用SM-LED的显示基板的制造中的故障最小化的目的,如果LED电极的基板界面可以最大化的平坦则将是有利的。

## 发明内容

[0015] 本文描述的是直径在10到150µm之间的微型发光二极管 (LED) 结构,其适合大面积阵列的流体组装以制造高分辨率的红-绿-蓝 (RGB) 显示器。微型LED的制造工艺与通过常规金属-有机化学气相沉积 (MOCVD) 生长技术生产的基于氮化镓 (GaN) 的蓝/绿色LED和基于磷化铝镓铟 (A1GaInP) 的红色LED兼容。所得的微型LED具有电极结构,该电极结构可在流体组装之后电性和物理结合显示基板中的阵列接触点以形成主动或被动矩阵显示器。所公开的微型LED结构能够在不改变微型LED的结构的情况下在满足不同显示要求的范围内改变像素亮度,从而不影响流体组装工艺的产量和可靠性。

[0016] 因此,提供了一种用于制造表面贴装(SM)微型LED(µLED)的方法。该方法在生长基板上提供了MOCVD-LED结构。一叠层覆盖生长基板,该生长基板包括具有在第一平面中的顶

表面的第一掺杂半导体、覆盖具有在第二平面中的顶表面的第一掺杂半导体的多量子阱 (MQW) 层以及覆盖MQW层且在第三平面中具有顶表面的第二掺杂半导体,其中第一和第二掺杂半导体被相反地掺杂有n和p掺杂剂,参见图1A和2A。在氮化镓微型LED的情况下,第一和第二掺杂半导体是掺杂的GaN。在砷化镓 (GaAs) 微型LED的情况下,第一和第二掺杂半导体可以是掺杂的磷化镓 (p-GaP) 或掺杂的磷化铟镓 (n-GaInP)。

[0017] 该方法蚀刻MOCVD叠层以在生长基板上形成多个单个的芯片。通过首先选择性地蚀刻上述叠层从每个芯片制造μLED。电绝缘体被保形地沉积以在覆盖蚀刻叠层的第四平面中形成顶表面,然后被选择性地蚀刻以暴露第二掺杂半导体,以产生第一过孔。还执行选择性蚀刻以暴露第一掺杂半导体,从而形成第二过孔。第一电极形成为覆盖第一过孔并通过第一过孔连接第二掺杂半导体,并在第五平面中具有基板界面表面。第二电极形成为覆盖第二过孔并通过第二过孔连接第一掺杂半导体,并在第五平面中具有基板界面表面。最后,将制成的μLED与生长基板分离。由于使用了常规的MOCVD晶片,LED具有与第一、第二和第三平面共面的最大横截面150微米,与第一、第二和第三平面正交于的平台叠层高度小于2微米,第五平面的平均平面度公差小于10纳米。

[0018] 更明确地,该方法能够通过选择性地蚀刻叠层以形成由暴露第一掺杂半导体的沟槽包围的中心平台叠层和由暴露第一掺杂半导体的周边沟槽谷分割的周边叠层,从而制造SM中心发光μLED。然后,将电绝缘体保形地沉积在蚀刻叠层上包括形成覆盖中心平台叠层和周边叠层的第四平面。选择性刻蚀以暴露第二掺杂半导体的步骤包括:刻蚀覆盖中心平台叠层的电绝缘体的一部分以形成第一过孔,而选择性蚀刻以暴露第一掺杂半导体的步骤包括:蚀刻覆盖周边沟槽谷的电绝缘体以形成第二个过孔。结果,第一电极覆盖中心平台叠层,并且通过第一过孔连接第二掺杂半导体,第二掺杂半导体在第五平面中具有基板界面表面。第二电极具有形成在周边沟槽谷上的第一部分,并通过第二过孔连接第一掺杂半导体。第二电极具有第二部分(与第一部分连接),该第二部分覆盖形成在周边叠层上的电绝缘体,并在第五平面中具有基板界面表面。

[0019] 通过选择性蚀刻叠层以形成中心平台叠层来形成SM周边发光μLED,该中心平台叠层通过暴露第一掺杂半导体的沟槽而与周边叠层分离。共形沉积的电绝缘体覆盖中心平台叠层和周边叠层。选择性蚀刻以暴露第二掺杂半导体的步骤包括:蚀刻覆盖周边叠层的电绝缘体的一部分以暴露第二掺杂半导体,且选择性蚀刻以暴露第一掺杂半导体的步骤包括:蚀刻电绝缘体的一部分、以及中心平台叠层中第二掺杂半导体和MQW层的下层部分以暴露第一掺杂半导体。结果,第二电极形成为覆盖中心平台叠层并通过第二过孔连接第一掺杂半导体。第一电极形成为覆盖在周边叠层上形成的电绝缘体之上,并且通过第一过孔连接第二掺杂半导体。

[0020] 通过选择性地蚀刻叠层以形成平台叠层和在平台叠层中且暴露第一掺杂半导体的周边沟槽谷,从而制造出SM-µLED全区域发光µLED。选择性蚀刻以暴露第二掺杂半导体的步骤包括:蚀刻电绝缘层覆盖平台叠层的一部分,以暴露第二掺杂半导体。选择性蚀刻以暴露第一掺杂半导体的步骤包括:蚀刻覆盖周边沟槽谷的电绝缘体。第一电极覆盖平台叠层并通过第一过孔连接第二掺杂半导体。第二电极包括覆盖周边沟槽过孔的第一部分,并通过第二过孔连接第一掺杂半导体。第二电极的第二部分(与第一部分连接)覆盖形成在平台叠层的周边上的电绝缘体,并且在第五平面中具有基板界面表面。

[0021] 还提供了具有非平面基板电极界面表面的发光显示基板。显示器由具有平面的顶表面和形成列和行导线阵列的LED交叉点控制矩阵的支撑基板组成。第一薄膜层覆盖支撑基板的顶表面,并且包括多个阱。每个阱具有凸的底表面,连接相应的列线的第一基板电极和连接相应的行线的第二基板电极。第二薄膜层插在支撑基板顶表面和第一薄膜层之间。阱底部凸的表面由插在支撑基板顶表面和第二薄膜层之间且位于每个阱底部下方的垫片形成。

[0022] 下面将提供上述方法的其他详细信息,以及中心、周边、全区域发光SM微型LED装置以及具有凸的阱底表面的发光基板。

### 附图说明

[0023] 图1A至1C是描绘用于一般照明目的的GaN-LED晶片(现有技术)的图。

[0024] 图2A和图2B是示出用于制造红色发光指示器的砷化镓(GaAs) LED晶片(现有技术)的图。

[0025] 图3A和3B分别描绘了传统封装的蓝色和红色LED(现有技术)的局部截面图。

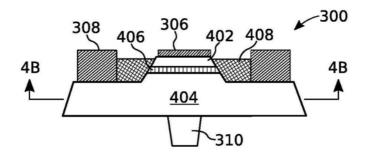

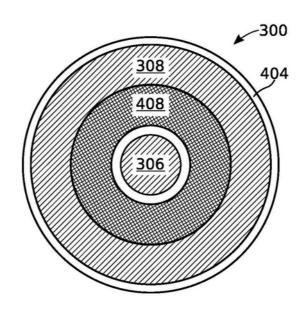

[0026] 图4A和图4B分别是能够用作表面贴装(SM) LED的发光元件的局部截面图和平面图。

[0027] 图5是描绘图4的LED的替代方案的局部截面图。

[0028] 图6A至图6J描绘了如美国专利9,825,202中所述的制造微型LED的步骤。

[0029] 图7A至图7C描绘了悬浮介质向具有导航龙骨(支柱)的微型LED施加扭矩。

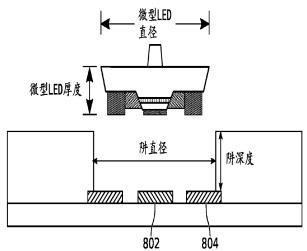

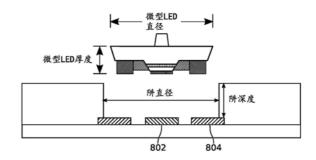

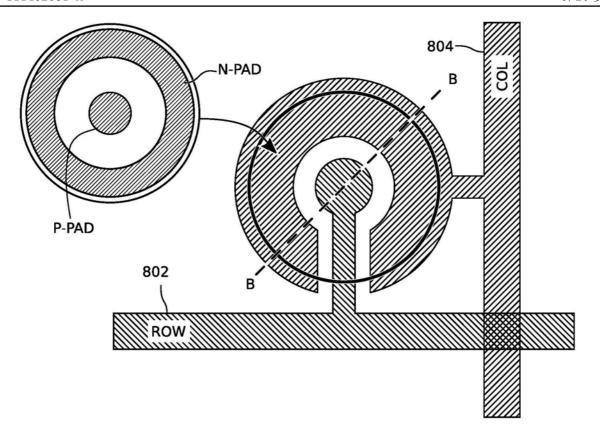

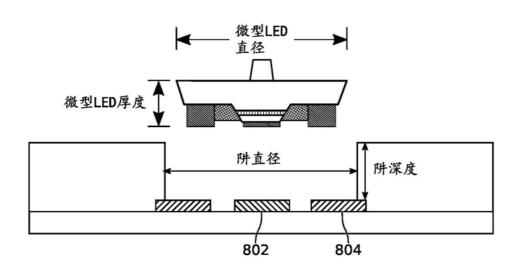

[0030] 图8A和8B分别是微型LED子像素布局的平面图和局部截面图。

[0031] 图9A至9E是描绘示例性阱变化中的微型LED对位的局部横截面图。

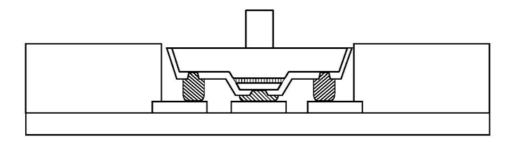

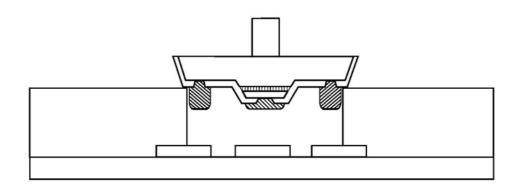

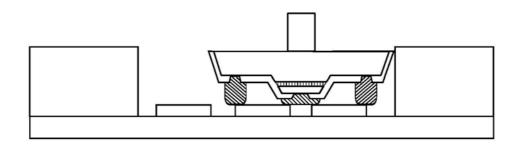

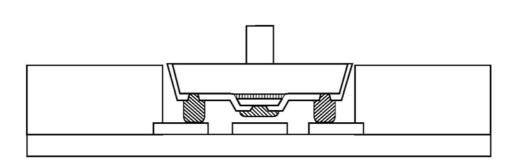

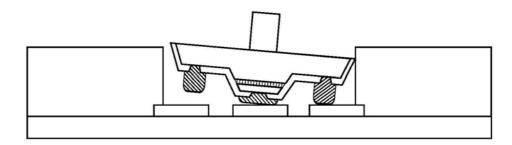

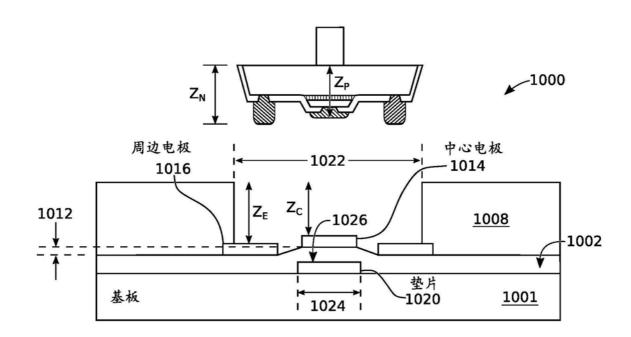

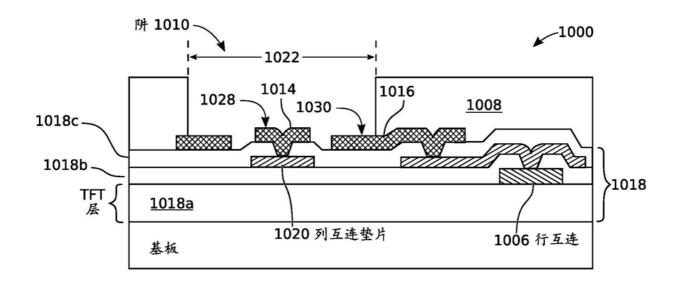

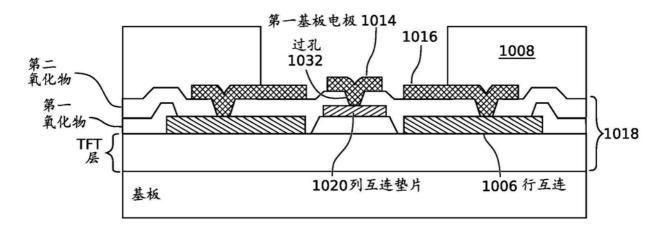

[0032] 图10A至图10C是基板阱和配合的微型LED的局部截面图,示出了阱底表面垫片。

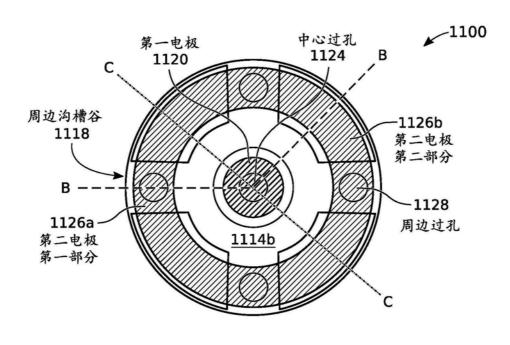

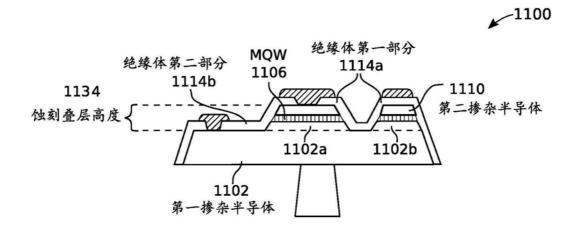

[0033] 图11A至图11D分别是平面SM中心发光µLED的平面图、两个局部截面图和透视图。

[0034] 图12是示出作为电流密度的函数的通量和效率之间的关系的图。

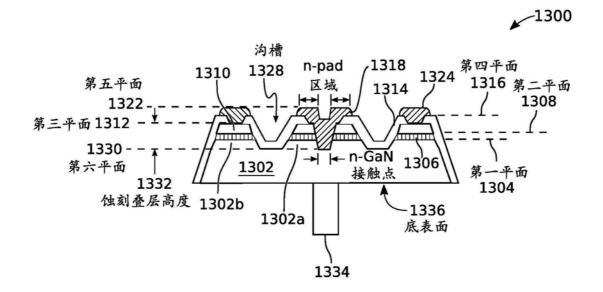

[0035] 图13A和13B分别是描绘平面SM周边发光μLED的平面图和局部截面图。

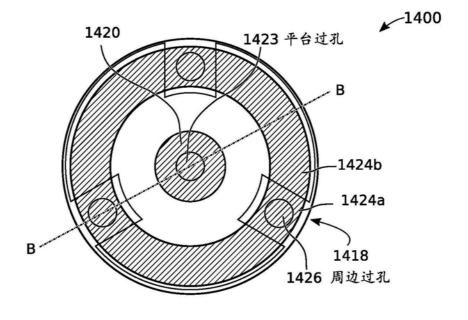

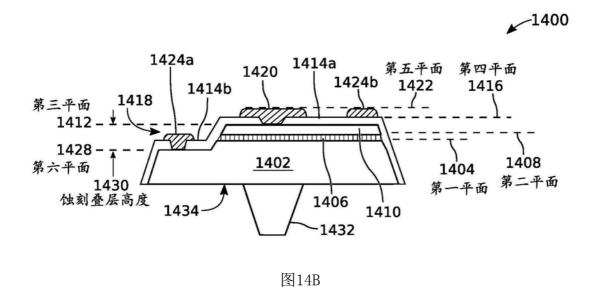

[0036] 图14A和图14B分别是平面SM全区域发光µLED的平面图和局部截面图。

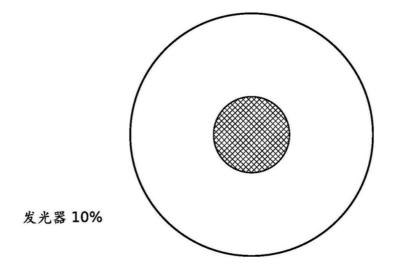

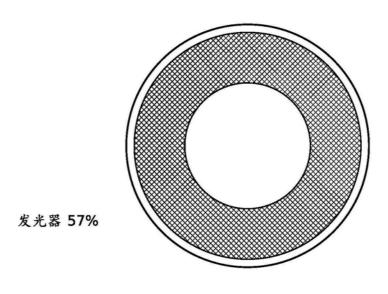

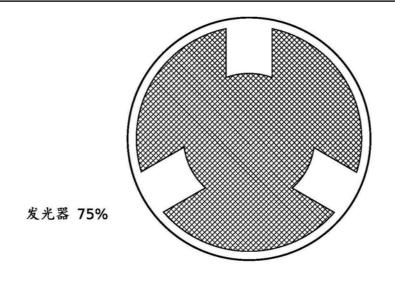

[0037] 图15A至图15C是比较中心发光(图11A)、周边发光(图13A)和全区域发光(图14A)的微型LED的发光表面积的平面图。

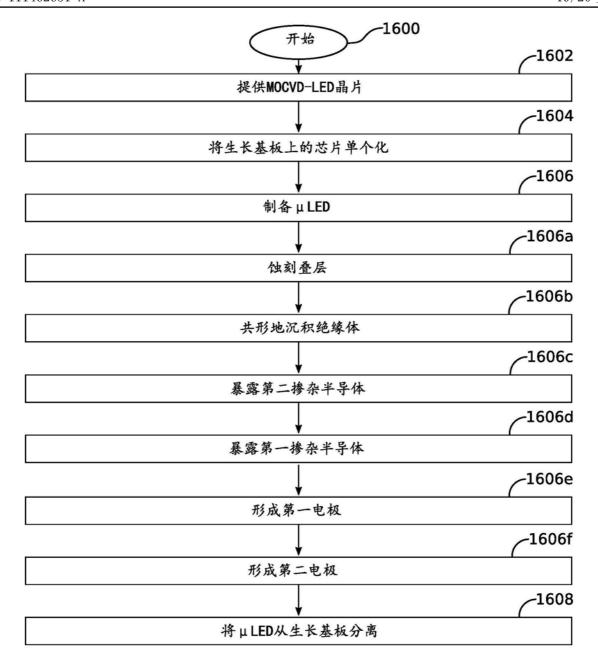

[0038] 图16是示出用于制造SMuLED的方法的流程图。

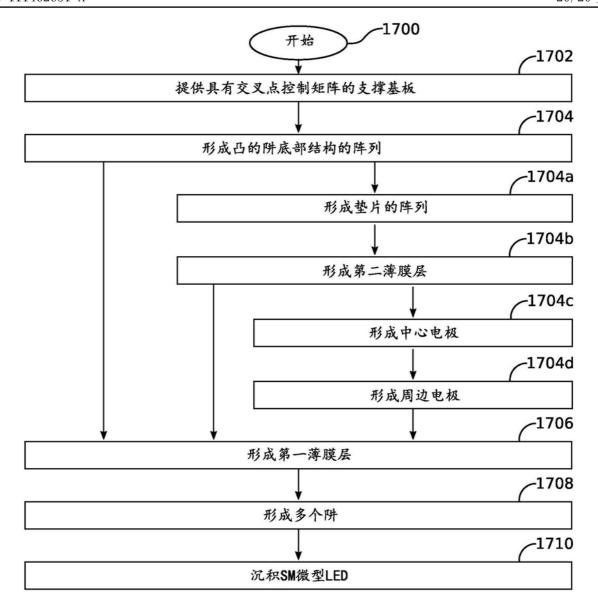

[0039] 图17是示出用于制造具有阱底表面垫片的显示基板的方法的流程图。

[0040] 主要元件符号说明

[0041]SM-LED300[0042]第一电接触点306[0043]第二电接触点308[0044]第二半导体层402[0045]第一半导体层404

[0046] MQW层 406、1106、1306

[0047] 电绝缘体 408、1314

[0048] 行线 802

| [0049] | 列线       | 804            |

|--------|----------|----------------|

| [0050] | 发光显示基板   | 1000           |

| [0051] | 支撑基板     | 1001           |

| [0052] | 支撑基板顶表面  | 1002           |

| [0053] | 第一薄膜层    | 1008           |

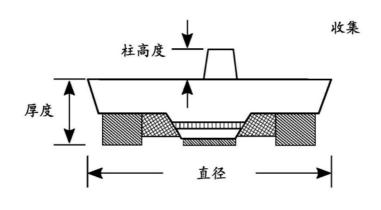

| [0054] | 阱        | 1010           |

| [0055] | 凸的底表面    | 1012           |

| [0056] | 第一基板电极   | 1014           |

| [0057] | 第二基板电极   | 1016           |

| [0058] | 第二薄膜层    | 1018           |

| [0059] | TFT层     | 1018a          |

| [0060] | 第一氧化物层   | 1018b          |

| [0061] | 第二氧化物层   | 1018c          |

| [0062] | 垫片       | 1020           |

| [0063] | 直径       | 1022           |

| [0064] | 宽度       | 1024           |

| [0065] | 顶面       | 1026           |

| [0066] | 第一电界面表面  | 1028           |

| [0067] | 第二电界面表面  | 1030           |

| [8800] | 过孔       | 1032           |

| [0069] | 中心发光µLED | 1100           |

| [0070] | 第一掺杂半导体  | 1102,1302,1402 |

| [0071] | 中心平台     | 1102a、1302a    |

| [0072] | 周边       | 1102b、1302b    |

| [0073] | 第二掺杂半导体  | 1110,1310,1410 |

| [0074] | 电绝缘体第一部分 | 1114a、1414a    |

| [0075] | 电绝缘体第二部分 | 1114b、1414b    |

| [0076] | 周边沟槽谷    | 1118,1418      |

| [0077] | 第一电极     | 1120、1318、1420 |

| [0078] | 中心过孔     | 1124、1320      |

| [0079] | 第二电极第一部分 | 1126a、1424a    |

| [0800] | 第二电极第二部分 | 1126b、1424b    |

| [0081] | 周边过孔     | 1128、1326、1426 |

| [0082] | 沟槽       | 1130、1328      |

| [0083] | 蚀刻叠层高度   | 1134、1332、1430 |

| [0084] | 第一平面     | 1104、1304、1404 |

| [0085] | 第二平面     | 1108、1308、1408 |

| [8800] | 第三平面     | 1112、1312、1412 |

| [0087] | 第四平面     | 1116、1316、1416 |

|        |          |                |

| [8800] | 第五平面            | 1122、1322、1422 |

|--------|-----------------|----------------|

| [0089] | 第六平面            | 1132、1330、1428 |

| [0090] | 导航龙骨或柱          | 1136、1432      |

| [0091] | 微型LED           | 1300,1400      |

| [0092] | 第二电极            | 1324           |

| [0093] | 第一掺杂半导体基底底表面    | 1336、1434      |

| [0094] | 平台过孔            | 1423           |

| [0095] | 具体实施方式将结合上述附图进- | 一步说明本发明。       |

# 具体实施方式

[0096] 使用无机LED和在显示器底板上的流体组装制造微型发光二极管 (µLED)显示器的一般方法被在先家族专利申请(美国专利号9,825,202,申请号15/412,73)所公开,其通过引用并入本文。特别是,美国专利9,825,202中图17的说明中描述了制造合适的显示器底板的工艺流程。在图16的说明中提出了流体组装的几何要求。本文所述的装置是对以上引用的在先家族专利申请中所讨论的表面贴装的微型LED结构的改进,其简化了装置的制造,同时提高了微型LED显示器的产量和多功能性。

[0097] 美国专利第9,825,202号描述了两种类型的氮化镓 (GaN) 微型LED。图4A和图4B中示出了在装置的中心处具有发光区域的结构,且具有发光器在外环中的结构被示出在图5中,如下所述。

[0098] 图4A和图4B分别是能够用作表面安贴装 (SM) LED的发光元件的局部截面图和平面图。SM-LED300包括具有n型掺杂剂或p型掺杂剂的第一半导体层404。第二半导体层402使用在第一半导体层404中未使用的掺杂剂类型。多量子阱 (MQW) 层406插在第一半导体层404和第二半导体层402之间。MQW层406通常可以为未示出的一系列量子阱层 (通常为5层,例如,将5nm的氮化铟镓 (InGaN) 与9nm的n掺杂GaN (n-GaN) 交替排列)。在MQW层和p掺杂半导体层之间可能还存在一个氮化铝镓 (A1GaN) 电子阻挡层 (未示出)。外部半导体层可以是约200nm厚的p掺杂GaN (Mg掺杂)。如果在MQW中使用较高的铟含量,则可以形成高亮度的蓝色LED或绿色的LED。最实用的第一半导体层材料和第二半导体层材料是能够发蓝光或绿光的GaN或能够发红光的磷化铝镓铟 (A1GaInP)。

[0099] 第二电接触点308被配置为环状,且第一半导体层404具有周边在第二电接触点环下方的盘形。第一电接触点306形成在第二电接触点308的环周内,且第二半导体层402和MQW层406是位于第一电接触点下面的叠层。一条沟槽可形成在第二电接触点308的环和第一电接触点306之间,并被电绝缘体408填充。

[0100] 常规的LED工艺(例如用于照明的LED)仅在与蓝宝石基板分离之前在一个表面上发生。其中一些工艺使用激光剥离(LLO)来将LED与蓝宝石基板分离作为最后一步。其他工艺不使用LLO,而是切出蓝宝石基板以将LED单个化。但是,SM-LED体系结构要求在与柱(导航龙骨)相对的表面上有电极,以便在将山LED从生长基板上移除后再制成柱。当从蓝宝石上移除LED时常规工艺无法提供维持每个LED已知位置的方法,因此可以在LED底部进行光刻。需要精确的x-y位置才能将柱准确地定位在LED顶表面上的所需位置(例如在中心)。需要精确的z(垂直)位置才能建立用于光刻的焦平面,以通过流体组装所需的尺寸控制(例如,表

面方向)对柱结构成像。即,SM-LED之LLO要求须以受控方式将SM-LED放置在转移基板上以 形成其柱,然后将其从转移基板上释放以制成用于流体组装的悬浮液。

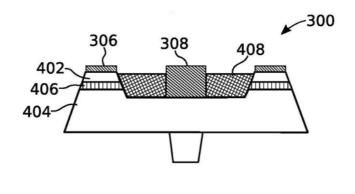

[0101] 图5是描绘图4A的LED的替代方案的局部截面图。在这个方面,第一电接触点(电极)306被配置为环,且第二半导体层402和MQW层406是在第一电接触点下方的环形的叠层。第二电接触点308形成在第一电接触点306的环周内。第一半导体层404具有中心部分位于第二电接触点下方的圆盘形状。如图所示,一条沟槽形成在第一电接触点306的环和第二电接触点308之间。电绝缘体408填充该沟槽。

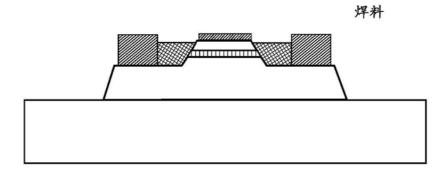

[0102] 图6A至图6J描绘了如美国专利9,825,202中所述的制造微型LED的步骤。为了描述的一致性,相对于生长基板定义了微型LED的顶和底表面,这是在MOCVD工艺中生长的最后一层,具有电极,底面具有可选择性的柱。因此,用于连接基板的表面贴装构造是底侧向上的。为简单起见,假定MOCVD叠层中的底层为n-GaN,顶层为p-GaN,但是当然,相反的结构也是可能的,可以适当选择掺杂和电极功函数。对于GaN和GaAs变体,图6A至6J示意性示出的示例性制造工艺流程基本上相同,过程如下:

[0103] 1)如上所述,LED叠层通过MOCVD被沉积在蓝宝石晶片上。可以使用其他基板,例如碳化硅(SiC)或硅,但蓝宝石基板允许通过激光剥离(LL0)从生长基板中移除μLED,从而使与蓝宝石基板相邻的底部器件表面的GaN分解。MQW结构被调整以产生所需的发光颜色,并且所得结构的厚度在2到7μm之间。也参见图1A是各个层的示例。

[0104] 2) 电流扩散层被沉积在p-GaN表面上。成分通常是薄的NiO<sub>x</sub>界面层加上透明的导电氧化物,例如铟锡氧化物(ITO),其厚度可能为100至500纳米(nm)。

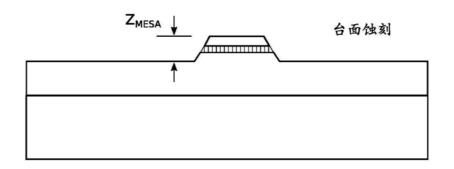

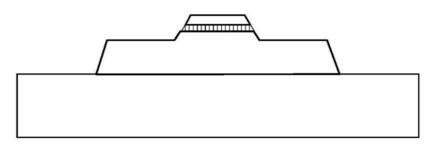

[0105] 3)发光区域通过光刻法被界定,且MOCVD叠层被蚀刻到延伸到n掺杂GaN层中的深度。取决于MOCVD结构,蚀刻深度(Z<sub>MESA</sub>)可以为300nm至2微米(μm)。通常小于1微米。

[0106] 4) µLED区域通过光刻被界定,然后整个叠层被向下蚀刻到蓝宝石基板。通常,图案是紧密排列的微型LED阵列以最大程度地提高微型LED在一块MOCVD晶圆上的产量。微型LED的尺寸被选择以匹配显示基板上的俘获位点的宽度,并且直径通常在15至150µm的范围内。

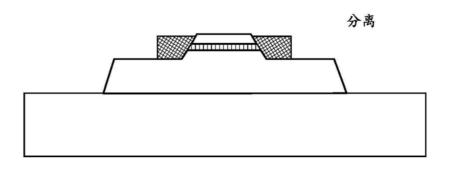

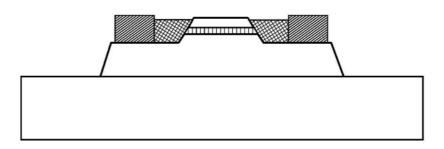

[0107] 5) 绝缘层,可以是SU8或可光图案化的聚酰亚胺,被沉积并被图案化,以防止N-pad和P-pad之间发生电流泄漏。

[0108] 6) 光刻图案被形成以防止金属沉积在N-pad区域之外,并且金属层被沉积以建立电极以匹配P-pad的高度。选择第一层以匹配n掺杂的GaN的功函数,可以是10至50nm厚的Ti或Cr。通过沉积适当厚度的金以匹配活性区台面的高度来完成堆积。

[0109] 7) 金属和光阻剂通过剥离被去除,在n-GaN接触区域上留下堆积。

[0110] 8) 光刻被进行以防止沉积在N-pad和P-pad接触区域之外,且金属叠层被沉积以连接uLED接触孔。

[0111] a. 第一金属被选择作为堆积物和焊料材料之间的导电层,可以是总厚度为100-200nm的铬/金 (Cr/Au) 或钛/镍 (Ti/Ni)。

[0112] b. 顶层是可以粘结到基板电极上的低熔点的焊料。一种系统是锡(Sn)合金,例如锡-铟(Sn-In)、锡-铟-银(Sn-In-Ag)、和锡-银-锑(Sn-Ag-Sb),其中选择的焊料金属类似于常规的低熔点焊料材料。另一种金属焊料系统是金/锗(Au/Ge)。

[0113] 9) 多余的金属通过剥离工艺被移除。

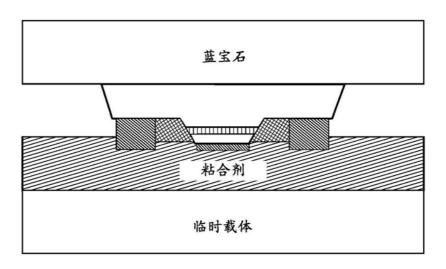

[0114] 10) 将完成的晶圆顶面侧用粘合剂层粘合到临时载体上,并通过LL0(laser

liftoff,激光剥离)去除蓝宝石生长晶圆。

[0115] 11) 现在,µLED为底部朝上在适用于进一步处理的平面阵列中的临时载体上。为了清楚起见,维持了基于原始生长取向来识别微型LED的顶表面和底表面的约定。

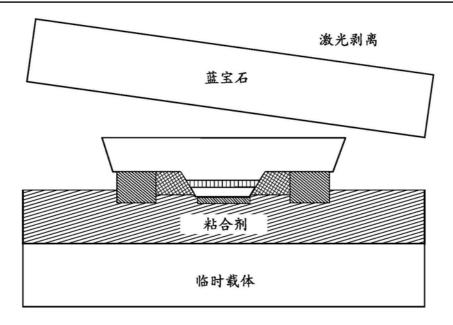

[0116] 12) 可选地,n-GaN可被蚀刻以减小微型LED的厚度。

[0117] 13) 用于流体组装的柱结构,也称为导航龙骨,可在微型LED中心附近的底部上被制造。柱可以是圆柱形的、圆锥形的或凹入的形状,其中柱的高度和直径被选择为便于在流体组装过程中µLED的底侧朝上的取向,如下面更详细地解释的。

[0118] 14) 最后,通过使用合适的溶剂溶解粘合剂,完整的µLED被收集到悬浮液中。

[0119] 由制造过程产生的微型LED均具有关键尺寸,例如直径、厚度和柱高,以及电极的尺寸和排列,这些尺寸被配置为与显示基板上的阱和电极的几何形状匹配,因此微型LED可与P-pad和N-pad电极组装并结合在一起,而P-pad和N-pad电极分别连接显示基板的行和列界面。如图8A和图8B所示,每个子像素在基板上都具有以具有垂直壁(也称为阱)的陷阱结构为中心的两个电极。盘形的微型LED以及匹配的圆形阱和电极被简单示出,但是可以使用诸如正方形或三角形的其他形状,只要该形状被设计为匹配基板中的互补形状,使得两个微型LED电极都电性连接正确的基板电极而不短路。

[0120] 通过在显示基板上方的液体悬浮液中分配微型LED来进行微型LED的流体组装。悬浮液组分的一些实例包括水、醇、酮、烷烃和有机酸。流体会受到某些方式的干扰,例如刷子或刀片,或溶剂或气体流,从而在整个基板上产生液体流。随着微型LED在基板上移动,随着微型LED被捕获并固定在基板阱结构中以创建自组装的微型LED阵列精确定位其表面贴装电极与基板阱中的电界面(基板电极)的接触,会进行许多捕获尝试。当流体组装完成时,由可使用摄像头和机器视觉算法确定组装成品率的现场监控系统确定,悬浮液被移除,并通过退火以在微型LED与基板电极之间形成焊料结合来完成显示器。流体组装本质上是一个随机过程,因此,根据捕集效率的统计分析来选择装置和捕集阱的尺寸以及组装过程的参数。

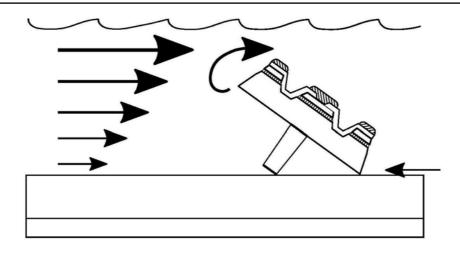

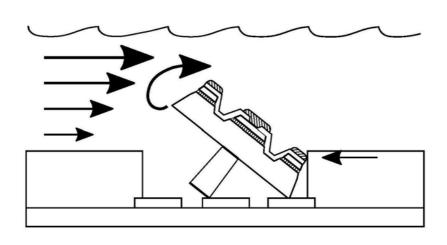

[0121] 图7A至图7C描绘了悬浮介质向具有导航龙骨(支柱)的微型LED施加扭矩。众所周知,流体速度在封闭表面从零开始抛物线增加,因此微型LED上的力随着与基板顶表面距离的增加而增加。当悬浮液首先分布在基板上时,在沉降到基板表面上之前微型LED可以相对快速地被分配。到达基板后,微型LED在流体流的影响下继续移动,因此,如图1所示,如图7A所示的具有立柱向下的装置经历扭矩趋于使方向发生翻转,使得电极朝下,立柱朝上。类似地,如果微型LED在柱向下的情况下进入阱中(图7B),则柱会阻止盘被捕获,并且盘上的作用力倾向于将微型LED推出阱并翻转方向使电极向下。如果将微型LED捕获在阱中,如图7C所示,由于柱的横截面较小,流体流动产生的合力要小得多,因此脱困的可能性很低。成功的流体组装要求对微型LED进行适当的处理,以使其最稳定的配置也是与基板以正确的位置和方向结合。

[0122] 图8A和8B分别是微型LED子像素布局的平面图和局部截面图。显示阵列中的每个微型LED子像素由施加到分别布置在行线802和列线804的交叉点矩阵中的两个电极的电压驱动。在典型的平板显示器制造中,行和列互连线是厚度在200至1500nm之间的铝或铜薄膜。给定的微型LED发出的光量由外部驱动器芯片提供的电流量以及作为子像素一部分的TFT控制电路(未示出)的电阻控制。用于制造微型LED的关键点在于,SM微型LED上的两个电

极须与低电阻的基板电极结合,以允许正确量的电流流过微型LED。基板电极被选择是为了实现低电阻以及与微型LED上的焊料层兼容。在一种情况下,基板电极是200至1000nm厚的铜,以与锡基焊料层形成铜-锡金属间化合物。当然,相反的布置,其中在基板电极上具有焊料且在微型LED上具有金电极,也是可能的。从图8B可以看出,成功的流体组装要求微型LED的直径小于阱的直径,因此微型LED可被捕获并与基板电极结合。

[0123] 图9A至9E是描绘示例性阱(well)变化中的微型LED对位的局部横截面图。图9A描绘了阱直径稍微大于微型LED直径,这有利于对准和结合。图9B中,由于阱太小而导致不利的对准和结合,从而阻止了微型LED与基板之间的电性接触。图9C中,阱直径太大,以至于允许LED电极引起行和列基板电极之间的短路。

[0124] 所有这些尺寸都是使用相对常规的光刻工艺通过光罩设计、膜厚和光阻剂曝光来控制尺寸的结果。用于堆积的沉积厚度被选择以匹配台面蚀刻的深度(参见图6B),该深度定义了中心活性(发光)区,因此须通过测量蚀刻深度来确定目标厚度。GaN蚀刻是在单个晶圆蚀刻腔室中被执行的,因此蚀刻速率在连续的晶圆之间可以相差10-20%。另外,蚀刻速率在整个晶片上不是完全均匀,从中心到边缘还有多达10-15%的变化。结果,对于标称目标为1微米的蚀刻,中心台面(ZMESA)的高度差异可能高达400nm。堆积金属的沉积通常是通过蒸发或溅射来完成的,通常是在批处理中将许多晶片一起加工,因此每个晶片的单独沉积厚度是不可行的。对于这种情况,无论上述蚀刻的差异如何,都将堆积沉积的目标厚度选择为所有晶片的ZMESA平均值,且结果对于某些晶片而言堆积的厚度太大,而对于其他晶片而言则太薄。由于GaN蚀刻和堆积金属沉积的变化,最终结构N-pad(连接n+半导体的电极)和P-pad(连接p+半导体的电极)可能不在同一平面上。这种差异在一个微型LED到另一个微型LED之间会有所不同,并且可能多达600nm,这可能会对微型LED和基板接触点之间的电性连接的良率和可靠性产生明显的负面影响。

[0125] 图9D中,周边的微型LED之N-pad太厚,因此微型LED的中心电极(P-pad)不会与基板电接口接触,因为N-pad和P-pad的高度不共面。结果是由于对电极平面性的控制不当而导致像素变暗。相反,图9E中,周边上的N-pad相对于中心电极太"低",导致电极与匹配的基板的电接口不完全接触。倾斜的微型LED导致N-pad和基板电极之间的接触被限制在一个很小的区域,而不是整个周边。小面积的接触会增加串联电阻并降低电性连接的可靠性。为了防止所描述的对准和结合失效机制,以使P-pad和N-pad电极始终处于正确的相对共面高度的方式制造微型LED,以实现与基板电极的最佳接触将是有利的。

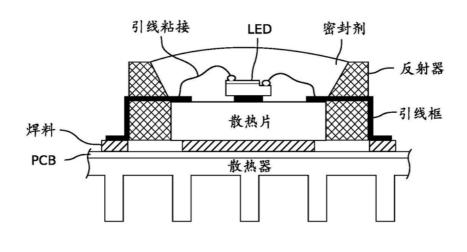

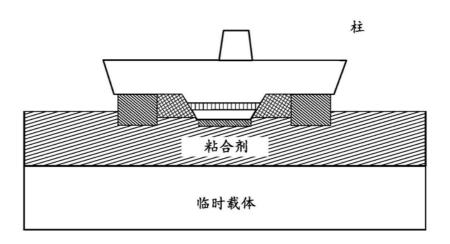

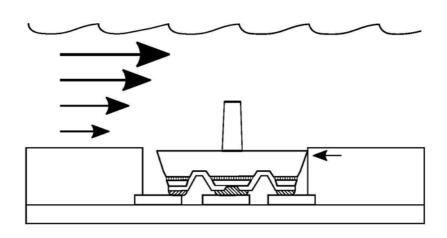

[0126] 图10A至图10C是基板阱和配合的微型LED的局部截面图,示出了阱底表面垫片。发光显示基板1000包括具有平坦的顶表面1002的支撑基板1001和包括列和行导线的阵列的LED交叉点控制矩阵。由于仅示出了一个LED,因此仅存在一对列线和行线,分别在图8A中以804和802示出。主动和被动矩阵系统被具体解释在先家族申请美国专利9,825,202中,其通过引用加入本文。如以上背景技术部分中所述,发光显示基板通常包括数百万个LED。第一薄膜层1008覆盖在支撑基板顶表面1002上。再次,仅示出了单个阱1010。每个阱1010具有由参考标号1012表示的凸的底表面,其中底表面具有连接相应的列线(804,见图8A)的第一基板电极1014和连接相应的行线(802,图8A)的第二基板电极1016。

[0127] 第二薄膜层1018插在支撑基板顶表面1002和第一薄膜层1008之间。如图10B和10C 所示,第二薄膜层1018可以由TFT层1018a组成,该TFT层1018a包含未示出的薄膜晶体管

(TFT),并且互连到一行列导线,为了使LED能工作。第二薄膜层1018也可以由一些氧化物或绝缘层构成,以第一氧化物层1018b和第二氧化物层1018c为例。垫片1020插在支撑基板顶表面1002和第二薄膜层1018之间,在每个阱底部下方。垫片1020可以是绝缘材料,如图10A所示,或电导体,如图10B和10C所示。第一薄膜层阱1010每个具有直径1022或横截面(在非圆形LED的情况下)。垫片1020具有小于直径1022的宽度1024和顶面1026。阱之凸的底表面1012是由于垫片顶面1026和支撑基板顶表面1002之间的高度差。

[0128] 如所有示例中所示,第一基板电极1014是中心基板电极,其具有用于电连接微型 LED的第一电界面表面1028,且第二基板电极1016是具有第二电界面表面1030的周边基板电极,比第一电接口表面更低,这是相对于支撑基板顶表面1002所界定的,也用于电连接微型LED。如图10B和10C明确所示,将垫片直接形成在列线上,从而形成列互连垫片1020。第一基板电极1014是覆盖过孔1032的中心基板电极,并连接列互连垫片1020。

[0129] 几种方法可被用来使微型LED电极与显示基板上的电接口结构匹配,以促进焊料结合。如图所示,可以将附加的垫片结构添加到中心基板电极下方的基板上,以通过垫片层的厚度使其在对外环基板电极上方升高。垫片可以由其他地方用于互连的金属膜制成,例如铝或铜,或者由绝缘层制成,且厚度可为50至500nm。如果垫片是导电的,则如图所示其通过层间电介质与中心基板电极隔离。可替代地,中心和边缘基板电极可用具有不同厚度的层被分别制造。结果是中心电极和边缘电极不再共面,并且高度差为 $D_{\text{sub}}=Z_{\text{C}}-Z_{\text{E}}$ (图10A)。可以看出,当电极高度 $D_{\text{LED}}=Z_{\text{P}}-Z_{\text{N}}$ 等于 $D_{\text{SUB}}$ 时,基板电极结构与微型LED最匹配。因此,这种结构可在 $D_{\text{LED}}$ <( $D_{\text{SUB}}$ )的任何情况下补偿"低" $P_{\text{P}}$ -pad (中心)电极,但以增加复杂性和可变性为代价。当然,对于具有"高" $P_{\text{P}}$ -pad电极 ( $D_{\text{LED}}>0$ )的微型LED,该结构将具有较低的性能,并导致接触面积减小,如图9E所示。

[0130] 只要基板电极的高度通常为50至500nm,且高度差适合与微型LED接口,则可以以各种方式来制造垫片。在主动矩阵显示器的情况下(例如图10B),在用于制造TFT(未示出)的层上构造微型LED布线。微型LED布线由以行和列排列的金属互连线组成,这些金属互连线连接基板界面电极。为低电阻行和列互连线通常为铜或铝,并且线的厚度为100至900nm。因此,由于金属层被绝缘层(通常为氧化硅)隔开,因此电极连接可以彼此通过而不会发生短路。图10B中,第一氧化物层1018b将列和行互连线(804和802,见图8A)分开,而第二氧化物层1018c将列互连和第一基板电极分开,并且层之间的连接通过适当放置的过孔来实现。图10B中,位于中心基板电极下方的垫片是由与用于制造列互连线的金属膜相同的金属制成的,因此通过该膜的厚度使中心基板电极被提升。图10C中,使用替代策略,其中通过第一氧化物层和列互连层的厚度使中心基板电极的高度增加。

[0131] 使用上述垫片,具有"高"周边电极的微型LED,如图9D所示,可以成功地与图10A,10B和10C所示的凸的阱底结构匹配。然而,即使微型LED的中心电极和周边电极是平面的,如图9A所示,或者微型LED中心电极比周边电极"更高",如图9E所示,微型LED电极将能够与基板电极连接,但代价是更高的电流电阻和减小的接触面积。

[0132] 本文更详细地公开了一种更简单且更有效的方法来制造具有相等(共平面)基板界面表面的微发光二极管电极。为了避免与先蚀刻MOCVD叠层的部分然后沉积和图案化薄膜有关的公差问题,固有地共面的MOCVD叠层有利地用作机械组件,以将N-pad电极提升到与P-pad相同的高度,确保DLED=0。GaN和AlGaInP的MOCVD生长是异质外延的过程,其中晶体

结构是由基础结构作为模板逐层建立的。与上述物理沉积过程不同,上述物理沉积过程通常会因晶粒生长而导致拓扑变化,而异质外延成功导致其表面在最多几个原子层内局部(小于或等于微型LED直径)平坦(平面)。类似地,绝缘层,通常是通过电浆增强化学气相沉积法沉积的二氧化硅,是平滑的并且局部(如上所定义)是平面的。因此,用作表面贴装电极的基底的第四平面基本上具有较低的可变性,通常小于10纳米。如上所述的具有低熔点焊料的表面贴装电极沉积在第四平面上,且最终电极界面表面位于同一第五平面上。电极沉积厚度的整体可变性会导致不同厚度的微型LED,但是当局部考虑时,所有微型LED的两个表面贴装电极界面表面均在同一(第五个)平面上。与CVD工艺不同,金属的物理气相沉积(PVD)会导致焊料表面由于结块和晶粒生长而具有一定的粗糙度。因此,最终表面的表面粗糙度可能约为10至100nm。考虑到该潜在的表面粗糙度,可以说微型LED电极界面表面具有10nm的平均第五平面公差。由于微型LED的制造使得DLED始终为零,因此图10的垫片结构没有优势,且参照图10,可以用DSUB=0来制造显示基板。

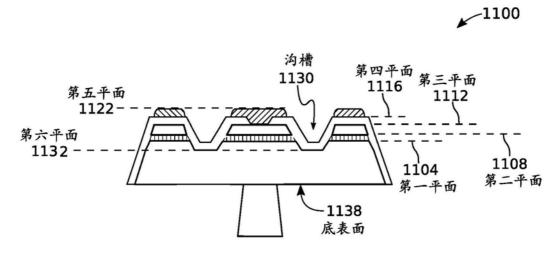

[0133] 图11A至图11D分别是平面SM中心发光µLED的平面图、两个局部截面图和透视图。中心发光µLED1100包括形成为基底并掺杂有n或p掺杂剂的第一掺杂半导体1102。如图11A和11C所示,在该示例中第一掺杂半导体1102基底具有圆形的周边,但是不限于任何特定形状。第一掺杂半导体1102具有形成在第一平面1104中的顶表面,该第一平面1104包括与周边1102b(由单独的虚线区分)分开的中心平台1102a(由虚线区分)。MQW层1106(通常形成为几个子层)具有在第二平面1108中形成的顶表面,该顶表面覆盖第一掺杂半导体中心平台1102a和周边1102b。掺杂有与在第一掺杂半导体1102中使用的掺杂剂相反的掺杂剂的第二掺杂半导体1110形成为具有在MQW层1106上方的第三平面1112中的顶表面的层。

[0134] 电绝缘体具有形成为具有覆盖第二掺杂半导体1110的第四表面1116中的顶表面的层的第一部分1114a,以及覆盖划分周边1102b的周边沟槽谷1118的第二部分1114b。绝缘体的关键功能是防止第一和第二掺杂半导体之间的电流泄漏。第一电极1120覆盖中心平台,通过中心过孔1124连接第二掺杂半导体1110,并且在第五平面1122中具有基板界面表面。第二电极具有形成在周边沟槽谷1118上的第一部分1126a,并且通过周边过孔1128连接第一掺杂半导体1102。第二电极具有覆盖在电绝缘体第一部分1114a的周边上的第二部分1126b,并连接第二电极第一部分,且在第五平面1122中具有基板界面表面。

[0135] SM中心发光µLED1100还包括形成在第一掺杂半导体1102中的沟槽1130,其将中心平台1102a与周边1102b分开。沟槽1130和周边沟槽谷1118具有形成在位于第一平面1104下方的第六平面1132中的顶表面。

[0136] 一方面,第一掺杂半导体1102和第二掺杂半导体1110是掺杂的GaN。或者,第一掺杂半导体1102和第二掺杂半导体1110是p掺杂的磷化镓(p-GaP)或n掺杂的磷化铟镓(n-GaInP)。从技术上讲,掺杂的半导体也可以是n-GaP和p-GaInP,但实用性较差。

[0137] 尽管未明确示出,但是如本领域所公知的,GaN装置可以可选地包括电子和空穴注入和阻挡层。在GaAs装置的情况下,可选的p和n包覆层可被使用,这也是本领域众所周知的。通常,对于红色和蓝色微型LED,都希望最大化电子和空穴在MQW层中的停留时间。例如仅考虑阳极侧,期望防止电子离开,因此电子阻挡层(A1GaN)对导带中的电子具有高势垒。还希望空穴容易进入,因此可以在电子阻挡层上添加单独的空穴注入层以消除价带中的小的不连续性。在A1GaInP情况下,n和p包覆层具有相同的目的,但出于历史原因,它们被称为

窗口和包覆层。如图所示,SM中心发光μLED1100可包括由多个周边沟槽谷1118分隔开的多个第一掺杂半导体周边段1102b。在那种情况下,MQW层1106、第二掺杂半导体1110和电绝缘体第一部分1114a覆盖每个第一掺杂半导体周边段1102b。第二电极第一部分1126a形成在每个周边沟槽谷1118上,并通过相应的周边过孔1128连接第一掺杂半导体1102。第二电极第二部分1126b覆盖电绝缘体第一部分1114a的分段的周边且在第五平面1122中具有基板界面表面。

[0138] 第一掺杂半导体1102、MQW层1106和第二掺杂半导体1110形成蚀刻叠层,蚀刻叠层具有与第一平面1104、第二平面1108和第三平面1112正交的高度1134小于2微米,并且第一、第二、第三和第四平面的平面度公差小于10纳米。如上所述,第五平面中的电极界面表面具有小于10nm的平均平面度公差。不是依靠使用薄膜堆积工艺来形成平面电极表面所固有的更大的公差,如图6A-6J所示,本文所述的装置使用MOCVD叠层的预先存在的平坦表面。因此,即使在晶片上的芯片之间或晶片之间的叠层蚀刻中存在差异,MOCVD平面也可用来维持最终形成的电极的基板界面之间的平坦性。简而言之,微型LED1100、以及下面呈现的微型LED1300和1400可被描述为一种装置,其中电极形成在蚀刻的MOCVD晶片(即蚀刻叠层)上,而没有随后沉积的介入的半导体层。

[0139] 在未示出的一个方面中,焊料层形成第一和第二电极界面表面的一部分,并且由诸如铟/锡(In/Sn)或金/锗(Au/Ge)的合金制成。可替代地,第一电极和第二电极的基板界面表面是金的。可选地,如图所示,导航龙骨或柱1136被附接到第一掺杂半导体基底底表面1138上。

[0140] 如图11A所示,该示例性的中心发光器设计使用环形的N-pad电极的四个等间隔的岛状结构支撑段。设计中的一个关键因素是N-pad和P-pad电极共面。还请注意,岛(周边)结构不具有电活性,且通过绝缘体与N-pad电极隔离,因此与N-pad电极的连接是通过在岛之间隔开的4个接触点进行的。岛的数量通常取决于微型LED的尺寸,从一到六个或更多,但是在岛状结构中设有至少一个用于与N掺杂区域接触的开口。较少的接触允许更大的面积用于焊料接触基板电极,但是增加了n掺杂层中的扩散电阻。相反,岛之间的开口越多,用于使微型LED与基板电极之间接触的最终面积越小。一方面,已经发现三个或四个岛/接触点为优选的以在串联电阻和结合强度之间取得最佳折衷。

[0141] 本发明的工艺流程类似于上面提出的现有技术流程,其中去除了与N-pad堆积相关的照片、沉积和剥离步骤(上述步骤6和7),因此在生产具有完美共面表面贴装电极的微型LED时降低了成本和复杂性。制造当前设计的基于GaN的微型LED的示例性工艺流程如下:

[0142] 1)如上所述,LED叠层通过MOCVD被沉积在蓝宝石晶片上。可以使用其他基板,例如SiC或硅,但是蓝宝石基板允许通过激光剥离(LL0)从生长基板中移除μLED。MQW结构被调整以产生所需的发光颜色且所得结构的厚度在2到7μm之间,另请参见图1A。

[0143] 2) 电流扩散层被沉积在p-GaN表面上。该成分通常是薄的 (10nm或更小) Ni O<sub>x</sub>界面层加上厚度可为100至500nm的透明导电氧化物,例如ITO。

[0144] 3) 发光区域通过光刻法被界定,且MOCVD叠层被蚀刻到延伸到n掺杂GaN层中的深度,从而形成本文中称为"蚀刻叠层"的结构。

[0145] 4) 通过光刻和将整个叠层向下蚀刻到蓝宝石基板来界定此ED区域。

[0146] 5) 一绝缘层,通常是厚度为100至400nm的等离子增强CVD (PECVD) 的二氧化硅

- (SiO<sub>2</sub>),被沉积以防止装置上电流泄漏。

- [0147] 6) 与p-GaN和n-GaN区对应的接触点被开设在绝缘层中。

- [0148] 7) 光刻图案被形成以防止金属沉积在N-pad和P-pad接触区域之外,且金属叠层被沉积以连接μLED接触孔。

- [0149] a. 第一金属层被选择为了与氧化物粘合,并且功函数与n掺杂的GaN相匹配。典型的材料是10至50nm厚的Cr。

- [0150] b. 下一种金属被选择作为粘附层和焊料材料之间的导电阻挡层,可以是总厚度为100-200nm的Cr/Au或Ti/Ni。

- [0151] c. 顶层是可以粘结基板电极的低熔点的焊料。一种系统是用于焊料熔化温度的锡合金。另一种金属系统是Au/Ge。

- [0152] d.可替代地,微型LED可以仅接收来自步骤7a和7b的金属,而低熔点焊料可以形成在显示基板电极上。

- [0153] 8) 多余的金属通过剥离工艺被去除。

- [0154] 9) 将完成的晶片顶面通过粘合剂层与临时载体粘结,并通过LL0移除蓝宝石生长晶片。

- [0155] 10) 现在, µLED以适合于进一步处理的平面阵列在载体晶圆上底面朝上。

- [0156] 11) 可选地,n-GaN可被蚀刻以减小µLED的厚度。

- [0157] 12) 用于流体组装的柱(导航龙骨)结构可选地被制造在μLED中心附近的底面上。柱可以是圆柱形、圆锥形或凹入的形状,其中柱的高度和直径经选择以利于在流体组装过程中μLED的底侧向上的取向。

- [0158] 13) 最后,通过使用合适的溶剂溶解粘合剂,完整的µLED被收集到悬浮液中。

- [0159] 由于红色LED是在不同的MOCVD工艺中制造的,因此针对GaAs基的装置修改了工艺流程。装置的形状以及电极和柱的位置与GaN装置的相似,但装置的厚度可能不同。示例性处理流程如下进行:

- [0160] 1) 如上所述,通过MOCVD LED叠层被沉积在GaAs晶片上。MQW结构被调整以产生所需的发光颜色,且所得结构的厚度在5到10μm之间。也参见图2A。

- [0161] 2) 可选地,p-GaP可被蚀刻以减小叠层的厚度。

- [0162] 3) 将完成的晶片顶面通过粘合剂层粘结玻璃或蓝宝石临时基板上,并通过湿蚀刻移除GaAs生长晶片。

- [0163] 4) µLED区域通过光刻被界定,整个叠层被蚀刻。

- [0164] 5)发光区域通过光刻法被界定,且MOCVD叠层被蚀刻到延伸到p掺杂的GaP层中的深度,从而形成蚀刻叠层。

- [0165] 6) 诸如Cr/Au的金属层被沉积在与该层的功函数匹配的p-GaP区域上。

- [0166] 7)诸如Ti/Au的金属层被沉积在与该层的功函数匹配的n-GaP区域上。

- [0167] 8) 沉积一层绝缘层,通常为100至400nm厚的PECVD的Si $0_2$ 被沉积以防止在装置上电流泄漏。

- [0168] 9) 在绝缘层中开设与p-GaP和n-GaP区域对应的接触点。

- [0169] 10) 光刻图案被形成以防止金属沉积在N-pad和P-pad接触区域之外,且金属叠层被沉积以连接μLED接触孔。

[0170] a.选择第一金属作为粘附层和焊料材料之间的导电阻挡层,其可以是总厚度为100-200nm的Cr/Au或Ti/Ni。

[0171] b. 顶层是可粘结基板电极的低熔点的焊料。一种系统是用于降低焊料的熔化温度的锡合金。另一种合适的低熔点金属系统是Au/Ge。或者,该焊料层可被形成在基板电极上。

[0172] 11)多余的金属通过剥离工艺被移除。

[0173] 12) 用粘合剂层将完成的晶片顶面粘合到临时晶片上,并通过溶解第一粘合剂移除第一临时基板。

[0174] 13) 现在, µLEDs以适合于进一步处理的平面阵列在临时晶片上底面朝上。

[0175] 14) 可选地,n-GaP可被蚀刻以减小微型LED的厚度。

[0176] 15) 用于流体组装的柱结构可选地制造在微型LED中心附近的底部。柱可以是圆柱形的、圆锥形的或凹入的形状,其中柱的高度和直径选择为利于在流体组装过程中使微型 LED的底部朝上的取向。

[0177] 16) 通过使用合适的溶剂溶解第二粘合剂,完成的微型LED被收集在悬浮液中。

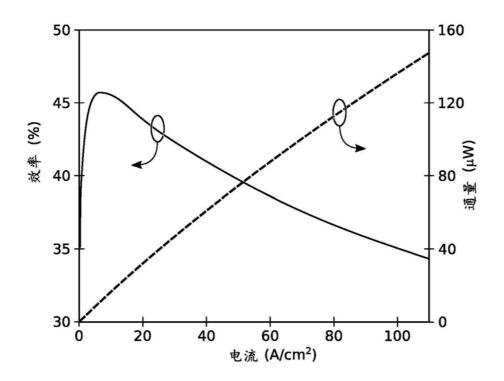

[0178] 图12是示出作为电流密度的函数的通量和效率之间的关系的图。微型LED显示器最重要的优点之一是无机LED可以实现非常高的亮度,这使灵活性能够使显示器的发光性能与产品的特定分辨率和亮度要求相匹配。小型可穿戴的显示器可能只需要150-200尼特(坎德拉每平方米)亮度,而电视可能是500-1500尼特,而户外公共信息显示器(PID)可能是2000-4000尼特。手机或平板电脑的小型显示器的分辨率可能超过600像素每英寸(ppi),而大型PID显示器的分辨率可能仅为20至60ppi,因此每个微型LED的可用面积也大不相同。对于发440nm(蓝光)的GaN微型LED,如图12所示,来自微型LED的光通量在相对较宽范围内是电流密度的近似线性函数。因此,微型LED显示器通过控制提供给每个子像素的电流来调节灰度强度。

[0179] 微型LED的电光转化效率(光输出/电功率)以相对较低的通量达到峰值,然后在很宽的施加电流范围内逐渐降低(下降)。对于显示器操作,期望在效率峰值附近操作以最小化显示器中散发的废热。但是,非常低的电流很难调节,因此给定显示器的最佳电流密度取决于多种因素。普通照明LED在大约70安培/平方厘米(A/cm2)的高电流密度下运行,以使每个装置的光输出最大化,从而使每个灯泡的成本最小化。微型LED显示器通常以较低的电流密度工作以实现更高的可靠性和更低的散热,因此工作范围可能在1到30A/cm²之间。影响微型LED配置选择的其他因素包括每个彩色微型LED的效率、色域要求以及以绿色为中心的人类视觉系统的灵敏度。因此,有利的是具有一种结构,该结构允许微型LED发光面积的调整,以平衡性能要求,同时保持固定的微型LED特性,例如柱高、厚度和直径,这对于高产量流体组装是至关重要的。

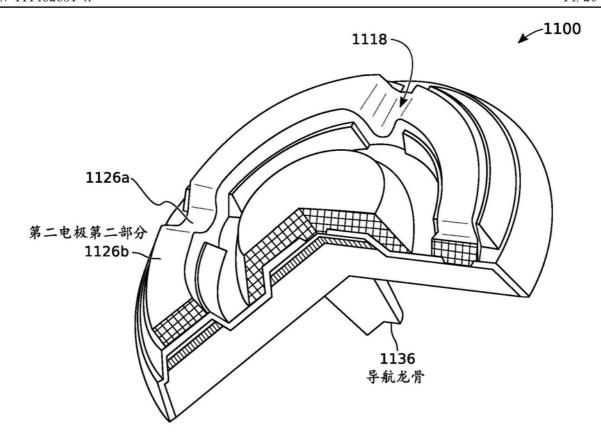

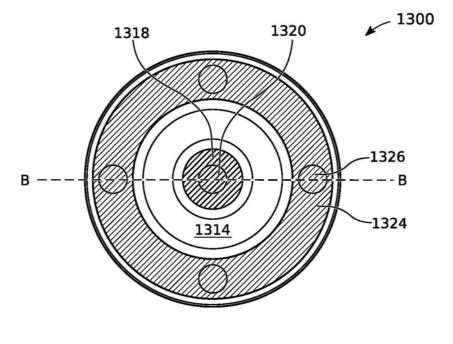

[0180] 图13A和13B分别是描绘平面SM周边发光μLED的平面图和局部截面图。周边发光μLED1300包括形成为基底并掺杂有n或p掺杂剂的第一掺杂半导体1302。第一掺杂半导体1302具有形成在包括与周边1302b分开的中心平台1302a的第一平面1304中的顶表面。如图13A所示,第一掺杂半导体基底是圆形的,但是其他众所周知的几何形状也是可能的。具有顶表面的MQW层1306形成在覆盖第一掺杂半导体中心平台1302a和周边1302b的第二平面1308中。掺杂有与用于第一掺杂半导体1302的掺杂剂相反的掺杂剂的第二掺杂半导体1310在覆盖MQW层1306的第三平面1312中具有顶表面。

[0181] 电绝缘体1314形成为在覆盖第二掺杂半导体1310的第四平面1316中具有顶表面的层。第一电极1318覆盖中心平台1302a,并通过中心过孔1320连接第一掺杂半导体1302。第一电极1318在第五平面1322中具有基板界面表面。第二电极1324覆盖电绝缘体1314的周边,并且通过周边过孔1326连接第二掺杂半导体1310。第二电极1324在第五平面1322中具有基板界面表面。在第一掺杂半导体1302中形成沟槽1328,该沟槽1328将中心平台1302a与周边1302b分开。沟槽具有形成在第一平面1302下方的第六平面1330中的顶表面。一方面,第一掺杂半导体1302和第二掺杂半导体1310是掺杂的GaN。或者,第一掺杂半导体1302和第二掺杂半导体1310是掺杂的n-GaInP。第一掺杂半导体中心平台1302a、MQW层1306以及第二掺杂半导体1310形成经蚀刻叠层,蚀刻叠层具有垂直于第一平面1304、第二平面1308和第三平面1312的高度1332小于2微米,且对第一、第二、第三和第四平面的平面度公差小于10纳米。第五平面中的电极界面表面的平均平面度公差也小于10nm。

[0182] 一方面,未示出的,焊料层形成第一和第二电极界面表面的一部分,并由诸如In/Sn或Au/Ge的合金制成。或者,第一电极和第二电极的基板界面表面是金。可选地,如图所示,导航龙骨或柱1336附接第一掺杂半导体基底底表面1336。

[0183] 上面描述的并且在图11A和11C中示出的中心发光器包括:发光面积为盘状微型 LED的总表面积的10%至15%,其中微型LED的表面积平行于第一、第二和第三平面。如图 13A-13B所示,可以改变结构使得发光区域是被P-pad覆盖的外环结构,而中心岛(平台)是 对N-pad电极的机械支撑。在这个方面,发光面积可是微型LED盘表面积的约50%。这种结构的优点是连续的P-pad电极不会被接触孔打断,因此可以实现与基板界面电接触点的完整 360度环接触。在这种结构中,在扩散电阻和减小平台的面积之间进行了权衡,该扩散电阻通过增加中心接触面积而降低,而平台的面积使焊料与基板电极保持接触。

[0184] 图14A和图14B分别是平面SM全区域发光μLED的平面图和局部截面图。全区域发光μLED1400包括形成为基底且掺杂有n或p掺杂剂的第一掺杂半导体1402。尽管第一掺杂半导体基底被描绘为圆形,但是它不限于任何特定的几何形状。第一掺杂半导体1402具有形成在包括平台的第一平面1404中的顶表面。MQW层1406具有在覆盖第一掺杂半导体平台的第二平面1408中形成的顶表面。掺杂有与第一掺杂半导体中使用的掺杂剂相反的掺杂剂的第二掺杂半导体1410形成为在覆盖MQW层1406的第三平面1412中具有顶表面的层。具有第一部分1414a的电绝缘体形成为在覆盖第二掺杂半导体1410的第四平面1416中具有顶表面的层。第二绝缘体1414b覆盖第一掺杂半导体周边沟槽谷1418。

[0185] 第一电极1420覆盖该平台并通过平台过孔1423连接第二掺杂半导体1410。第一电极1420在第五平面1422中具有基板界面表面。第二电极具有覆盖周边沟槽谷1418的第一部分1424a。第二电极具有覆盖周边沟槽谷1418的第一部分1424a,且通过周边过孔1426连接第一掺杂半导体1402。第二电极第二部分1424b形成为覆盖在第五平面1422中具有基板界面表面的电绝缘体第一部分1414a的周边。第一掺杂半导体周边沟槽谷1418具有形成在位于第一平面1408下方的第六平面1428中的顶表面。

[0186] 一方面,第一掺杂半导体1402和第二掺杂半导体1410是掺杂的GaN。或者,第一掺杂半导体1402和第二掺杂半导体1410是p掺杂的p-GaP或n掺杂的n-GaInP。如图所示,SM全区域发光μLED可包括多个第一掺杂半导体周边沟槽谷1418。在那种情况下,第二电极第一部分1424a形成在每个周边沟槽谷1418上,且通过相应的周边过孔1426连接第一掺杂半导

体1402。第二电极第二部分1424b覆盖在第五平面1422中具有基板界面表面的电绝缘体第一部分1414a的周边部分。

[0187] 第一掺杂半导体1402、MQW层1406和第二掺杂半导体1410形成蚀刻叠层,该蚀刻叠层具有与第一平面1404、第二平面1408和第三平面1412正交的高度1430小于2微米,且具有第一、第二、第三和第四平面的平面度公差小于10纳米。第五平面中的电极界面表面的平均平面度公差也小于10nm。

[0188] 一方面,未示出的,焊料层形成第一和第二电极界面表面的一部分,并且由诸如 铟/锡(In/Sn)或金/锗(Au/Ge)的合金制成。或者,第一和第二电极的基板界面表面是金。可 选地,如图所示,导航龙骨或柱1432附接第一掺杂半导体基底底表面1434。

[0189] 图15A至图15C是比较中心发光(图11A),周边发光(图13A)和全区域发光(图14A)的微型LED的发光表面积的平面图。如果需要大的发光面积,则图14A的全发光器设计可被采用。活性发光区也是P-pad电极的机械支撑岛,因此使活性岛(平台)中的开口(显示3个)被形成以接触n-GaN区。在这种情况下,发光面积约为微型LED盘直径的75%。对于GaAs基的装置,与四接触点变体相比,三接触点几何形状通常更有利,因为在任何分裂平面上只有一个薄区域,从而使微型LED的机械强度更高。全发光结构的另一个优点是,对装置周边的蚀刻损伤对效率的影响较小。这对于A1GaInP装置尤其重要,在该装置中,由于蚀刻损坏而引起的表面重组会导致围绕LED周边的发光率降低,从而限制了小型微型LED的发光。

[0190] 本文所述的微型LED设计与常规MOCVD制造兼容,并且有利于流体组装以及与在同一平面上形成的表面贴装电极的结合。所述结构的另一个好处是可以灵活地将发光面积从微型LED面积的10%更改为75%,而无需更改对于成功进行流体组装至关重要的物理特性(直径、厚度、侧壁角度和接柱尺寸)。

[0191] 图16是示出用于制造SMuLED的方法的流程图。尽管为清楚起见该方法被描述为一系列编号的步骤,但是编号不一定指示步骤的顺序。应当理解,这些步骤中的一些可以被跳过,并行执行或在不要求维持严格顺序的情况下执行。然而,通常该方法遵循所描绘步骤的数字顺序。该方法始于步骤1600。

[0192] 步骤1602提供了一种MOCVD LED结构,该MOCVD LED结构包括生长基板、覆盖在包括在第一平面中具有顶表面的第一掺杂半导体的生长基板上的叠层、覆盖在第二平面中具有顶表面的第一掺杂半导体的MQW层、以及覆盖MQW层并在第三平面中具有顶表面的第二掺杂半导体,参见图1A和2A。第一和第二掺杂半导体相反地掺杂有n和p掺杂剂。上面提到了可以使用的明确的半导体材料。

[0193] 步骤1604蚀刻M0CVD叠层以在生长基板上形成多个单个的芯片。步骤1606如下从每个芯片制造µLED。步骤1606a选择性地蚀刻叠层。步骤1606b共形地沉积电绝缘体以在覆盖蚀刻叠层的第四平面上形成顶表面。步骤1606c选择性地蚀刻以暴露第二掺杂半导体,从而形成第一过孔。步骤1606d选择性地蚀刻以暴露第一掺杂半导体,从而形成第二过孔。

[0194] 注意:在某些情况下可在步骤1606c之前执行步骤1606d,或者在适当的光刻和图案化之后同时执行步骤1606d。步骤1606e形成覆盖第一过孔的第一电极,通过第一过孔连接第二掺杂半导体,且在第五平面中具有基板界面表面。步骤1606f形成覆盖第二过孔的第二电极,通过第二过孔连接第一掺杂半导体,并且在第五平面中具有基板界面表面。在一些方面,步骤1606e和1606f可以以相反的顺序执行或与适当的光刻和图案化同时执行。步骤

1608将制造的µLED与生长基板分离。

[0195] 一方面,该方法制造中心发光µLED,在这种情况下,选择性地蚀刻叠层(步骤1606a)包括创建被暴露第一掺杂半导体的沟槽包围的中心平台叠层,以及由暴露第一掺杂半导体的周边沟槽谷分割的周边叠层。在步骤1606b中将电绝缘体保形地沉积在经蚀刻叠层上包括形成覆盖中心平台叠层和周边叠层的第四平面。

[0196] 在步骤1606c中选择性地蚀刻以暴露第二掺杂半导体包括蚀刻覆盖中心平台叠层的电绝缘体的一部分以创建第一过孔,且在步骤1606d中选择性地蚀刻以暴露第一掺杂半导体包括蚀刻覆盖周边沟槽谷的电绝缘体以创建第二过孔。然后,在步骤1606e中形成第一电极包括形成覆盖中心平台叠层的第一电极,通过第一过孔连接第二掺杂半导体。在步骤1606f中形成第二电极包括:形成第二电极,该第二电极具有形成在周边沟槽谷上的第一部分,该第一部分通过第二过孔连接第一掺杂半导体,以及形成第二部分,该第二部分覆盖形成在周边叠层上的电绝缘体,具有在第五平面中的基板界面表面。

[0197] 另一方面,该方法通过选择性地蚀刻MOCVD叠层(步骤1606a)以产生通过暴露第一掺杂半导体的沟槽而与周边叠层分离的中心平台叠层,来制造周边发光山ED。在步骤1606b中保形地沉积电绝缘体包括形成覆盖中心平台叠层和周边叠层的第四平面。在步骤1606c中选择性地蚀刻以暴露第二掺杂半导体包括:蚀刻电绝缘体的覆盖周边叠层的一部分以暴露第二掺杂半导体。在步骤1606d中选择性蚀刻以暴露第一掺杂半导体包括:蚀刻电绝缘体的一部分以及中心平台叠层中的第二掺杂半导体和MQW层的下面部分,以暴露第一掺杂半导体。在步骤1606e中形成第一电极包括形成覆盖形成在周边叠层上的电绝缘体上且通过第一过孔连接第二掺杂半导体的第一电极。在步骤1606f中形成第二电极包括形成覆盖中心平台叠层且通过第二过孔连接第一掺杂半导体的第二电极。

[0198] 在另一变更中,该方法通过选择性地蚀刻MOCVD叠层(步骤1606a)以形成平台叠层和在平台叠层中以暴露第一掺杂半导体的周边沟槽谷,从而制造全区域发光μLED。步骤1606c中选择性地蚀刻以暴露第二掺杂半导体包括:蚀刻电绝缘体覆盖平台叠层的一部分以暴露第二掺杂半导体。步骤1606d中选择性地蚀刻以暴露第一掺杂半导体包括蚀刻覆盖周边沟槽谷的电绝缘体。步骤1606e中形成第一电极包括形成覆盖在平台叠层之上且通过第一过孔连接第二掺杂半导体的第一电极。步骤1606f中形成第二电极包括:形成第二电极的第一部分,该第一部分覆盖通过第二过孔连接第一掺杂半导体的周边沟槽通孔;以及形成第二部分,该第二部分覆盖形成在平台叠层的周边的电绝缘体,且在第五平面中具有基板界面表面。

[0199] 如上所述,步骤1608制成µLED具有与第一平面、第二平面和第三平面共面的最大横截面150微米,与第一平面、第二平面和第三平面正交的平台叠层(蚀刻叠层)高度小于2微米,以及小于10纳米的平均第五平面的平面度公差。

[0200] 图17是示出用于制造具有阱底表面垫片的显示基板的方法的流程图。尽管为清楚起见,该方法被描述为一系列编号的步骤,但是编号不一定代表步骤的顺序。应当理解的,这些步骤中的一些可以被跳过、并行执行或在不要求严格顺序的情况下执行。然而,通常,该方法如上所述,并且通常遵循以下呈现的步骤的数字顺序。

[0201] 该方法开始于步骤1700。步骤1702提供具有平坦顶表面的支撑基板和包括列和行导线阵列的LED交叉点控制矩阵。步骤1704形成覆盖支撑基板顶表面的凸的阱底部结构的

阵列。步骤1706形成覆盖支撑基板顶表面和凸的阱底部结构的第一薄膜层。步骤1708形成在第一薄膜层中且暴露出凸的阱底部结构的阱。步骤1710流体沉积表面贴装微型LED于阱中。

[0202] 一方面,步骤1704中形成凸的阱底部结构的阵列包括:对于每个凸的阱底部结构, 形成电连接对应的列线的第一基板电极和电连接对应的行线的第二基板电极。另一方面, 形成第一薄膜层之前,步骤1704a形成覆盖支撑基板顶表面的垫片的阵列。垫片可以是导电的或绝缘的材料。步骤1704b形成覆盖垫片阵列的第二薄膜层。

[0203] 一方面,步骤1704a中形成垫片的阵列包括形成具有宽度和顶表面的垫片。然后,步骤1708中在第一薄膜层中形成阱包括形成具有大于垫片宽度的直径(横截面)的阱。阱的凸的底表面的形状响应于垫片顶表面和支撑基板顶表面之间的高度差。

[0204] 另一方面,步骤1704中形成凸的阱底部结构的阵列包括附加的子步骤。步骤1704c 形成具有用于电连接微型LED的第一电界面表面的中心第一基板电极。步骤1704d形成具有 第二电界面表面的周边第二基板电极,该第二电界面表面相对于支撑基板顶表面限定为低于第一电界面表面,用于电连接微型LED。

[0205] 又一方面,步骤1704a中形成垫片的阵列包括形成直接覆盖(与之电接触)列线的每个垫片,形成列互连垫片。然后,步骤1704b中形成第二薄膜层包括在覆盖每个列互连垫片的第二薄膜层中形成过孔,且在步骤1704c中形成中心第一基板电极包括形成覆盖过孔且电连接列互连垫片的中心第一基板电极。

[0206] 步骤1710中沉积表面贴装微型LED通常包括用具有顶部表面和基板界面表面的微型LED填充阱,该微型LED的顶表面具有中心第一电极和周边第二电极,该基板界面表面分别连接第一基板电极和第二基板电极。一方面,微型LED具有带有共面的基板界面表面的中心第一电极和周边第二电极,例如上面详细描述的中心发光、周边发光和全区域发光微型LED。或者,微型LED可具有非共面的中心第一电极和周边第二电极基板界面表面,如图9D和9E所示。

[0207] 平面表面贴装微型LED和相关的制造工艺已示出。特定的半导体材料、几何形状和明确的工艺步骤的示例已示出以说明本发明。然而,本发明不仅限于这些示例。本领域技术人员将想到本发明的其他变型和实施例。

图1A

图1B

图1C

图2A

图2B

图3A

图3B

图4A

图4B

图5

图6A

图6B

LED 蚀刻

图6C

图6D

图6E

图6F

# 粘结

图6G

图6H

图6I

图6J

图7A

图7B

图7C

图8A

图8B

图9A

图9B

图9C

图9D

图9E

图10A

图10B

图10C

图11A

图11B

图11C

图11D

图12

图13A

图13B

图14A

图15A

图15B

图15C

图16

图17

| 专利名称(译) | 用于表面贴装微型LED流体组装的发光显示基板及制备方法             |         |            |  |  |

|---------|-----------------------------------------|---------|------------|--|--|

| 公开(公告)号 | CN111462651A                            | 公开(公告)日 | 2020-07-28 |  |  |

| 申请号     | CN202010351855.4                        | 申请日     | 2020-04-28 |  |  |

| [标]发明人  | 保罗约翰舒勒<br>战长青<br>佐佐木健司<br>葛特鄂孟<br>李宗霑   |         |            |  |  |

| 发明人     | 保罗·约翰·舒勒<br>战长青<br>佐佐木健司<br>葛特鄂孟<br>李宗霑 |         |            |  |  |

| IPC分类号  | G09F9/33 H01L27/15                      |         |            |  |  |

| 优先权     | 16/406196 2019-05-08 US                 |         |            |  |  |

| 外部链接    | SIPO                                    |         |            |  |  |

|         |                                         |         |            |  |  |

### 摘要(译)

用于表面贴装微型LED流体组装的发光显示基板及其制备方法被提出。该发光显示基板包括:支撑基板,具有平面的顶表面以及包括列和行导线的阵列的发光二极管(LED)交叉点控制矩阵;第一薄膜层,覆盖所述支撑基板的顶表面且包括多个阱;其中,每个阱具有凸的底表面、与对应的列导线连接的第一基板电极、以及与对应的行导线连接的第二基板电极。